## Isolated 16-bit Analog I/O Board for PCI Express

### AIO-160802LI-PE

\* Specifications, color and design of the products are subject to change without notice.

This product is a PCI Express bus-compliant interface board used to provide an analog signal I/O function on a PC. AIO-160802LI-PE features bus isolated 16-bit analog input 8 channels and 16-bit analog output 2 channels.

Equipped with digital I/O and counter, this product is multifunction and bus isolated type that provides isolation between PC and external analog I/O circuit. This product carries buffer memory for 1K of data, allowing sampling to be performed in a variety of trigger / clock conditions.

Windows/Linux driver and full-fledged data logger software "C-LOGGER" is bundled with this product. Possible to be used as a data recording device for MATLAB and LabVIEW, with dedicated libraries.

#### **Features**

## Bus isolated high precision analog input 8 channels / output 2 channels, each 4 channels for digital I/O, counter 1 channel

This product has analog input ( $10\mu$ sec / channel, 16-bit, 8 channels), analog output ( $10\mu$ sec, 16-bit, 2 channels), analog I/O control signal (TTL level 6 channels), digital I/O (each 4 channels for TTL level), counter (32-bit, TTL level 1 channel).

## Functions and connectors are compatible with PCI compatible board ADAI16-8/2(LPCI)L

The functions same with PCI compatible board ADAI16-8/2(LPCI)L are provided. In addition, as there is compatibility in terms of connector shape and pin assignments, it is easy to migrate from the existing system.

## Bus isolation between PC and external analog input circuit by a digital isolator

Isolation between PC and external analog input circuit by a digital isolator improves noise performance.

## The start/end of sampling can be controlled by software, comparison of conversion data, an external trigger, etc.

You can select from software, comparison of conversion data or an external trigger to control the start of sampling. You can select from completion of sampling for a specified number of sessions, comparison of conversion data, an external trigger or software to control the end of sampling. The sampling cycle can be selected from the internal clock or an external clock.

## Equipped with buffer memory (1K data) that can be used in the FIFO or RING format

The analog input block contains buffer memory (1K data) that can be used in the FIFO or RING format. This allows for background analog I/O that does not depend on the operation status of the software or PC.

## Bus isolation between PC and external analog output circuit by a digital isolator

Isolation between PC and external analog output circuit by a digital isolator improves noise performance.

## The start/end of sampling can be controlled by software, an external trigger, etc.

You can select from software, an external trigger to control the start of sampling. You can select from completion of sampling for a specified number of sessions, an external trigger or software to control forcibly the end of sampling. The sampling cycle can be selected from the internal clock or an external clock.

## Safety design to adjust output voltage to 0V when power supply is turned on

To prevent the unstable voltage and the connected device of D/A converter from fault and malfunctions when the power supply is turned on, the circuit is designed to adjust output voltage of the analog output to 0V.

## Equipped with buffer memory (1K data) that can be used in the FIFO or RING format

The analog output block contains buffer memory (1K data) that can be used in the FIFO or RING format. This allows for background analog output that does not depend on the operation status of the software or PC.

## Digital filter function included to prevent misdetection due to chattering on external signals

A digital filter is included to prevent misdetection due to chattering on the control signal (external trigger input signal, sampling clock input signal, etc.), digital input signal and counter input signal. (Except from external clock input signal and counter gate signal)

#### Software-based calibration function

Calibration can be all performed by software. Apart from the adjustment information prepared before shipment, additional adjustment information can be stored according to the use environment.

## Data logger software, Windows/Linux compatible driver libraries are attached.

Using the bundled data logger software "C-LOGGER" allows you to display recorded signal data in graphs, save files without any special program. In addition, the driver library API-PAC(W32) which makes it possible to create applications of Windows/Linux is provided.

## MATLAB and LabVIEW is supported by a plug-in of dedicated library VI-DAQ.

Using the dedicated library MATLAB and VI-DAQ makes it possible to make a LabVIEW application.

### **Specification**

|                                             | Item                                                                                                                                                                                                                                                                                                    | Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Ana                                         | alog input                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| Ŀ                                           | solated specification                                                                                                                                                                                                                                                                                   | Bus-Isolated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| li                                          | nput type                                                                                                                                                                                                                                                                                               | Single-Ended Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| ١                                           | Number of input channels                                                                                                                                                                                                                                                                                | 8ch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| li                                          | nput range                                                                                                                                                                                                                                                                                              | Bipolar ±10V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| Α                                           | Absolute max. input voltage                                                                                                                                                                                                                                                                             | ±20V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| li                                          | nput impedance                                                                                                                                                                                                                                                                                          | $M\Omega$ or more                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| F                                           | Resolution                                                                                                                                                                                                                                                                                              | 16bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| Ν                                           | Non-Linearity error *1*2                                                                                                                                                                                                                                                                                | ±16LSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| (                                           | Conversion speed                                                                                                                                                                                                                                                                                        | 10μsec/ch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| E                                           | Buffer memory                                                                                                                                                                                                                                                                                           | 1k Word                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| C                                           | Conversion start trigger                                                                                                                                                                                                                                                                                | Software / external trigger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| C                                           | Conversion stop trigger                                                                                                                                                                                                                                                                                 | Number of sampling times / external trigger/software                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|                                             | External start signal                                                                                                                                                                                                                                                                                   | TTL-level (Rising or falling edge can be selected by software) Digital filter (1μsec can be selected by software)                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| E                                           | External stop signal                                                                                                                                                                                                                                                                                    | TTL-level (Rising or falling edge can be selected by software) Digital filter (1µsec can be selected by software)                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| E                                           | External clock signal                                                                                                                                                                                                                                                                                   | TTL-level (Rising or falling edge can be selected by software)                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| ۱na                                         | alog output                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| _                                           | solated specification                                                                                                                                                                                                                                                                                   | Bus-Isolated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| Ν                                           | Number of output channels                                                                                                                                                                                                                                                                               | 2ch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| C                                           | Output range                                                                                                                                                                                                                                                                                            | Bipolar ±10V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| Α                                           | Absolute max. input currency                                                                                                                                                                                                                                                                            | ±5mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|                                             | Output impedance                                                                                                                                                                                                                                                                                        | $1\Omega$ or less                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| F                                           | Resolution                                                                                                                                                                                                                                                                                              | 16bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|                                             | Non-Linearity error *1                                                                                                                                                                                                                                                                                  | ±5LSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| _                                           | Conversion speed                                                                                                                                                                                                                                                                                        | 10μsec                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| _                                           | Buffer memory                                                                                                                                                                                                                                                                                           | 1k Word                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| _                                           | Conversion start trigger                                                                                                                                                                                                                                                                                | Software / external trigger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| _                                           | Conversion stop trigger                                                                                                                                                                                                                                                                                 | Number of sampling times / external trigger/software                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|                                             | External start signal                                                                                                                                                                                                                                                                                   | TTL-level (Rising or falling edge can be selected by software)                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|                                             |                                                                                                                                                                                                                                                                                                         | Digital filter (1µsec can be selected by software)                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| E                                           | External stop signal                                                                                                                                                                                                                                                                                    | TTL-level (Rising or falling edge can be selected by software) Digital filter (1µsec can be selected by software)                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|                                             |                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| L                                           | External clock signal                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| E                                           | External clock signal                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| E                                           | ital I/O                                                                                                                                                                                                                                                                                                | TTL-level (Rising or falling edge can be selected by software)                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| E<br>Dig                                    | ital I/O Number of input channels Number of output                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| Dig<br>N                                    | ital I/O Number of input channels Number of output channels                                                                                                                                                                                                                                             | TTL-level (Rising or falling edge can be selected by software)  Unisolated input 4ch (TTL-level positive logic)                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| Dig<br>N<br>Cou                             | ital I/O Number of input channels Number of output channels unter                                                                                                                                                                                                                                       | TTL-level (Rising or falling edge can be selected by software)  Unisolated input 4ch (TTL-level positive logic)  Unisolated input 4ch (TTL-level positive logic)                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| Dig N                                       | ital I/O Number of input channels Number of output channels unter Number of channels                                                                                                                                                                                                                    | TTL-level (Rising or falling edge can be selected by software)  Unisolated input 4ch (TTL-level positive logic)  Unisolated input 4ch (TTL-level positive logic)  1ch                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| Dig<br>N<br>COL                             | ital I/O Number of input channels Number of output channels unter Number of channels Counting system                                                                                                                                                                                                    | TTL-level (Rising or falling edge can be selected by software)  Unisolated input 4ch (TTL-level positive logic)  Unisolated input 4ch (TTL-level positive logic)  1ch  Up count                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| Dig N                                       | ital I/O Number of input channels Number of output channels unter Number of channels Counting system Max. count                                                                                                                                                                                         | TTL-level (Rising or falling edge can be selected by software)  Unisolated input 4ch (TTL-level positive logic)  Unisolated input 4ch (TTL-level positive logic)  1ch  Up count  FFFFFFFF (Binary data,32bit)                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| Dig N c                                     | ital I/O Number of input channels Number of output channels unter Number of channels Counting system Max. count Number of external inputs                                                                                                                                                               | TTL-level (Rising or falling edge can be selected by software)  Unisolated input 4ch (TTL-level positive logic)  Unisolated input 4ch (TTL-level positive logic)  1ch  Up count  FFFFFFFh (Binary data,32bit)  2 TTL-level (Gate/Up)/ch  Gate (High level), Up (Rising edge)                                                                                                                                                                                                                                      |  |  |  |  |

| Dig N c                                     | ital I/O Number of input channels Number of output channels unter Number of channels Counting system Max. count Number of external inputs Number of external outputs                                                                                                                                    | TTL-level (Rising or falling edge can be selected by software)  Unisolated input 4ch (TTL-level positive logic)  Unisolated input 4ch (TTL-level positive logic)  1ch  Up count  FFFFFFF (Binary data,32bit)  2 TTL-level (Gate/Up)/ch  Gate (High level), Up (Rising edge)  TTL-level Count match output (positive logic, pulse output)                                                                                                                                                                          |  |  |  |  |

| Dig Col | ital I/O Number of input channels Number of output channels unter Number of channels Counting system Max. count Number of external inputs Number of external outputs Response frequency                                                                                                                 | TTL-level (Rising or falling edge can be selected by software)  Unisolated input 4ch (TTL-level positive logic)  Unisolated input 4ch (TTL-level positive logic)  1ch  Up count  FFFFFFFh (Binary data,32bit)  2 TTL-level (Gate/Up)/ch  Gate (High level), Up (Rising edge)                                                                                                                                                                                                                                      |  |  |  |  |

| Dig N o                                     | ital I/O Number of input channels Number of output channels unter Number of channels Counting system Max. count Number of external inputs Number of external outputs Response frequency mmon section                                                                                                    | TTL-level (Rising or falling edge can be selected by software)  Unisolated input 4ch (TTL-level positive logic)  Unisolated input 4ch (TTL-level positive logic)  1ch  Up count  FFFFFFF (Binary data,32bit)  2 TTL-level (Gate/Up)/ch  Gate (High level), Up (Rising edge)  TTL-level Count match output (positive logic, pulse output)  1MHz (Max.)                                                                                                                                                             |  |  |  |  |

| Dig N o Col N o F Cor N                     | ital I/O Number of input channels Number of output channels unter Number of channels Counting system Max. count Number of external inputs Number of external outputs Response frequency mmon section //O address                                                                                        | TTL-level (Rising or falling edge can be selected by software)  Unisolated input 4ch (TTL-level positive logic)  Unisolated input 4ch (TTL-level positive logic)  1ch  Up count  FFFFFFFF (Binary data,32bit)  2 TTL-level (Gate/Up)/ch  Gate (High level), Up (Rising edge)  TTL-level Count match output (positive logic, pulse output)  1MHz (Max.)                                                                                                                                                            |  |  |  |  |

| Dig Col N Col N F Col N                     | ital I/O Number of input channels Number of output channels unter Number of channels Counting system Max. count Number of external inputs Number of external outputs Response frequency mmon section //O address                                                                                        | TTL-level (Rising or falling edge can be selected by software)  Unisolated input 4ch (TTL-level positive logic)  Unisolated input 4ch (TTL-level positive logic)  1ch  Up count  FFFFFFF (Binary data,32bit)  2 TTL-level (Gate/Up)/ch  Gate (High level), Up (Rising edge)  TTL-level Count match output (positive logic, pulse output)  1MHz (Max.)                                                                                                                                                             |  |  |  |  |

|                                             | ital I/O Number of input channels Number of output channels unter Number of channels Counting system Max. count Number of external inputs Response frequency mmon section //O address Interruption level Connector                                                                                      | TTL-level (Rising or falling edge can be selected by software)  Unisolated input 4ch (TTL-level positive logic)  Unisolated input 4ch (TTL-level positive logic)  1ch  Up count  FFFFFFFF (Binary data, 32bit)  2 TTL-level (Gate/Up)/ch  Gate (High level), Up (Rising edge)  ITL-level Count match output (positive logic, pulse output)  1MHz (Max.)  64 ports  Errors and various factors, One interrupt request line as INTA 10250-52A2JL[3M]                                                                |  |  |  |  |

|                                             | ital I/O Number of input channels Number of output channels unter Number of channels Counting system Max. count Number of external inputs Response frequency mmon section //O address Interruption level Connector Power consumption                                                                    | TTL-level (Rising or falling edge can be selected by software)  Unisolated input 4ch (TTL-level positive logic)  Unisolated input 4ch (TTL-level positive logic)  1ch  Up count  FFFFFFFF (Binary data, 32bit)  2 TTL-level (Gate/Up)/ch  Gate (High level), Up (Rising edge)  TTL-level Count match output (positive logic, pulse output)  1MHz (Max.)  64 ports  Errors and various factors, One interrupt request line as INTA 10250-52A2JL[3M]  3.3VDC 820mA (Max.)                                           |  |  |  |  |

|                                             | ital I/O Number of input channels Number of output channels unter Number of channels Counting system Max. count Number of external inputs Number of external outputs Response frequency mmon section //O address Interruption level Connector Power consumption Operating condition                     | TTL-level (Rising or falling edge can be selected by software)  Unisolated input 4ch (TTL-level positive logic)  Unisolated input 4ch (TTL-level positive logic)  1ch  Up count  FFFFFFFF (Binary data, 32bit)  2 TTL-level (Gate/Up)/ch  Gate (High level), Up (Rising edge)  ITL-level Count match output (positive logic, pulse output)  1MHz (Max.)  64 ports  Errors and various factors, One interrupt request line as INTA 10250-52A2JL[3M]                                                                |  |  |  |  |

|                                             | ital I/O Number of input channels Number of output channels unter Number of channels Counting system Max. count Number of external inputs Response frequency mmon section //O address Interruption level Connector Power consumption Deparating condition                                               | TTL-level (Rising or falling edge can be selected by software)  Unisolated input 4ch (TTL-level positive logic)  Unisolated input 4ch (TTL-level positive logic)  1ch  Up count  FFFFFFFF (Binary data, 32bit)  2 TTL-level (Gate/Up)/ch  Gate (High level), Up (Rising edge)  TTL-level Count match output (positive logic, pulse output)  1MHz (Max.)  64 ports  Errors and various factors, One interrupt request line as INTA 10250-52A2JL[3M]  3.3VDC 820mA (Max.)                                           |  |  |  |  |

|                                             | ital I/O Number of input channels Number of output channels unter Number of channels Counting system Max. count Number of external inputs Number of external outputs Response frequency mmon section //O address Interruption level Connector Copwer consumption Deparating condition Bus specification | TTL-level (Rising or falling edge can be selected by software)  Unisolated input 4ch (TTL-level positive logic)  Unisolated input 4ch (TTL-level positive logic)  1ch  Up count  FFFFFFFF (Binary data, 32bit)  2 TTL-level (Gate/Up)/ch  Gate (High level), Up (Rising edge)  ITTL-level Count match output (positive logic, pulse output)  1MHz (Max.)  64 ports  Errors and various factors, One interrupt request line as INTA  10250-52A2JL[3M]  3.3VDC 820mA (Max.)  0 - 50°C, 10 - 90%RH (No condensation) |  |  |  |  |

- The non-linearity error means an error of approximately 0.1% occurs over the maximum

- range at 0°C and 50°C ambient temperature

- At the time of the source use of a signal which built in the high-speed operational amplifier.

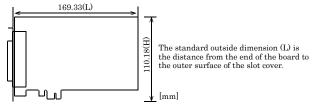

### **Board Dimensions**

### Support Software

#### Windows version of analog I/O driver API-AIO(WDM) [Stored on the bundled CD-ROM driver library API-PAC(W32)]

The API-AIO(WDM) is the Windows version driver library software that provides products in the form of Win32 API functions (DLL). Various sample programs such as Visual Basic and Visual C++, etc and diagnostic program useful for checking operation is provided.

< Operating environment >

Windows Vista, XP, Server 2003, 2000 OS Visual Basic, Visual C++, Visual C#, Adaptation language Delphi, C++ Builder

You can download the updated version from the CONTEC's Web site (http://www.contec.com/apipac/). For more details on the supported OS, applicable language and new information, please visit the CONTEC's Web site.

### Linux version of analog I/O driver API-AIO(LNX) [Stored on the bundled CD-ROM driver library API-PAC(W32)]

The API-AIO(LNX) is the Linux version driver software which provides device drivers (modules) by shared library and kernel version. Various sample programs of gcc are provided.

< Operating environment >

OS RedHatLinux, TurboLinux

> (For details on supported distributions, refer to Help available after installation.)

Adaptation language gcc

You can download the updated version from the CONTEC's Web site (http://www.contec.com/apipac/). For more details on the supported OS, applicable language and new information, please visit the CONTEC's Web site.

#### **Data Logger Software C-LOGGER** [Stored on the bundled CD-ROM driver library API-PAC(W32)]

C-LOGGER is a data logger software program compatible with our analog I/O products. This program enables the graph display of recorded signal data, zoom observation, file saving, and dynamic transfer to the spreadsheet software "Excel". No troublesome programming is required.

CONTEC provides download services (at

http://www.contec.com/clogger) to supply the updated drivers. For details, refer to the C-LOGGER Users Guide or our website.

< Operating environment >

Windows Vista, XP, Server 2003, 2000

### **Data Acquisition library for MATLAB ML-DAQ** (Available for downloading (free of charge) from the **CONTEC** web site.)

This is the library software which allows you to use our analog I/O device products on MATLAB by the MathWorks. Each function is offered in accordance with the interface which is integrated in MATLAB's Data Acquisition Toolbox.

See http://www.contec.com/mldag/ for details and download of ML-DAQ.

### Data acquisition VI library for LabVIEW VI-DAQ (Available for downloading (free of charge) from the **CONTEC** web site.)

This is a VI library to use in National Instruments LabVIEW. VI-DAQ is created with a function form similar to that of LabVIEW's Data Acquisition VI, allowing you to use various devices without complicated settings.

See http://www.contec.com/vidag/ for details and download of VI-DAQ.

### Cable & Connector

#### Cable (Option)

Shield Cable with 50-Pin Mini-Ribbon Connectors at either Ends

: PCB50PS-0.5P (0.5m)

: PCB50PS-1.5P (1.5m)

Shield Cable with 50-Pin Mini-Ribbon Connector at one End

: PCA50PS-0.5P (0.5m) : PCA50PS-1.5P (1.5m)

### **Accessories**

### **Accessories (Option)**

Screw Terminal Unit (M3 x 50P) : EPD-50A \*1\*2

**Buffer Amplifier Box**

for Analog Input Boards (8ch type) : ATBA-8L \*1\*4

**Buffer Amplifier Box**

for Analog Input Boards (16ch type) : ATBA-16L \*1\*4

BNC Terminal Unit (for analog input 8ch): ATP-8L \*1\*6

- \*1 PCB50PS-0.5P or PCB50PS-1.5P optional cable is required separately.

- \*2 "Spring-up" type terminal is used to prevent terminal screws from falling off.

- \*4 An external power supply is necessary (optional AC adaptor POA200-20 prepared.)

- \*6 Capable of using the analog input of up to 8ch, and analog output of up to 2ch.

- \* Check the CONTEC's Web site for more information on these options.

#### ⚠ CAUTION

It may affect the withstanding voltage depending on the cable and terminal unit to be used

### **Packing List**

Board [AIO-160802LI-PE] ...1 First step guide ... 1 CD-ROM \*1 [API-PAC(W32)] ...1

\*1 The CD-ROM contains the driver software and User's Guide.

#### How to connect the connectors

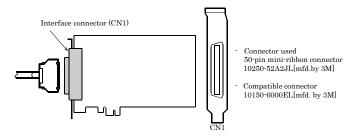

#### Connector shape

To connect an external device to this board, plug the cable from the device into the interface connector (CN1) shown below.

\* Please refer to page 3 for more information on the supported cable and accessories.

#### **Connector Pin Assignment**

## Pin Assignments of AIO-160802LI-PE Interface Connector (CN1)

| (CNT)                               | N.C.         |    |       | 0.5 | 10.00       | A 1 O - t t - 00                    |

|-------------------------------------|--------------|----|-------|-----|-------------|-------------------------------------|

| Non Connect                         | N.C.         | 50 |       | 25  | AO 00       | Analog Output 00                    |

| Analog Ground<br>( for AO )         | AGND         | 49 |       | 24  | AGND        | Analog Ground<br>( for AO )         |

| Non Connect                         | N.C.         | 48 |       | 23  | AO 01       | Analog Output 01                    |

| Analog Ground<br>(for AO)           | AGND         | 47 |       | 22  | AGND        | Analog Ground<br>( for AO )         |

| Analog Input 04                     | AI 04        | 46 |       | 21  | AI 00       | Analog Input 00                     |

| Non Connect                         | N.C.         | 45 |       | 20  | N.C.        | Non Connect                         |

| Analog Input 05                     | AI 05        | 44 | 50 25 | 19  | AI 01       | Analog Input 01                     |

| Non Connect                         | N.C.         | 43 |       | 18  | N.C.        | Non Connect                         |

| Analog Ground<br>( for AI )         | AGND         | 42 |       | 17  | AGND        | Analog Ground<br>( for AI )         |

| Analog Ground<br>( for AI )         | AGND         | 41 |       | 16  | AGND        | Analog Ground<br>( for AI )         |

| Analog Input 06                     | AI 06        | 40 |       | 15  | AI 02       | Analog Input 02                     |

| Non Connect                         | N.C.         | 39 |       | 14  | N.C.        | Non Connect                         |

| Analog Input 07                     | AI 07        | 38 |       | 13  | AI 03       | Analog Input 03                     |

| Non Connect                         | N.C.         | 37 |       | 12  | N.C.        | Non Connect                         |

| AO External Start<br>Trigger Input  | AO START     | 36 |       | 11  | AI<br>START | Al External Start<br>Trigger Input  |

| AO External Stop<br>Trigger Input   | AO STOP      | 35 |       | 10  | AI STOP     | Al External Stop<br>Trigger Input   |

| AO External Sampling<br>Clock Input | AO EXCLK     | 34 |       | 9   | AI<br>EXCLK | Al External Sampling<br>Clock Input |

| Digital Ground                      | DGND         | 33 | 26    | 8   | DGND        | Digital Ground                      |

| Digital Output 00                   | DO 00        | 32 | 26    | 7   | DI 00       | Digital Input 00                    |

| Digital Output 01                   | DO 01        | 31 |       | 6   | DI 01       | Digital Input 01                    |

| Digital Output 02                   | DO 02        | 30 |       | 5   | DI 02       | Digital Input 02                    |

| Digital Output 03                   | DO 03        | 29 |       | 4   | DI 03       | Digital Input 03                    |

| Digital Ground                      | DGND         | 28 |       | 3   | DGND        | Digital Ground                      |

| Counter UP Clock<br>Input           | CNT<br>UPCLK | 27 |       | 2   | CNT<br>GATE | Counter Gate Control<br>Input       |

| Reserved                            | Reserved     | 26 |       | 1   | CNT<br>OUT  | Counter Output                      |

| Analog Input00 - Analog Input07      | Analog input signal. The numbers correspond to channel numbers.                                                                  |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| Analog Output00 - Analog<br>Output01 | Analog output signal. The numbers correspond to channel numbers.                                                                 |

| Analog Ground                        | Common analog ground for analog I/O signals.                                                                                     |

| Al External Start Trigger Input      | External trigger input for starting analog input sampling.                                                                       |

| Al External Stop Trigger Input       | External trigger input for stopping analog input sampling.                                                                       |

| Al External Sampling Clock Input     | External sampling clock input for analog input.                                                                                  |

| AO External Start Trigger Input      | External trigger input for starting analog output sampling.                                                                      |

| AO External Stop Trigger Input       | External trigger input for stopping analog output sampling.                                                                      |

| AO External Sampling Clock Input     | External sampling clock input for analog output.                                                                                 |

| Digital Input00 - Digital Input03    | Digital input signal.                                                                                                            |

| Digital Output00 - Digital Output03  | Digital output signal.                                                                                                           |

| Counter Gate Control Input           | Gate control input signal for counter.                                                                                           |

| Counter Up Clock Input               | Count-up clock input signal for counter.                                                                                         |

| Counter Output                       | Counter output signal.                                                                                                           |

| Digital Ground                       | Common digital ground for digital I/O signals, external trigger inputs, external sampling clock inputs, and counter I/O signals. |

| Reserved                             | Reserved pin.                                                                                                                    |

| N.C.                                 | No connection to this pin.                                                                                                       |

#### **↑** CAUTION

Do not connect any of the outputs and power outputs to the analog or digital ground.

Neither connect outputs to each other. Doing either can result in a fault.

If analog and digital ground are shorted together, noise on the digital signals may affect the analog signals.

Accordingly, analog and digital ground should be separated.

Leave "Reserved" pins unconnected. Connecting these pins may cause a fault in the board.

### **Analog Input Signal Connection**

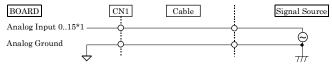

#### Single-ended Input

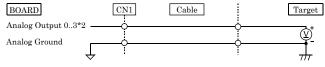

The following figure shows an example of flat cable connection. Connect separate signal and ground wires for each analog input channel on CN1.

#### Single-ended Input Connection (Flat Cable)

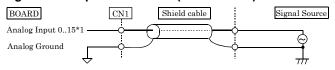

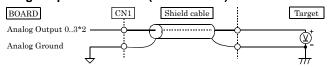

The following figure shows an example of shield cable connection. Use shielded cable if the distance between the signal source and board is long or if you want to provide better protection from noise. For each analog input channel on CN1, connect the core wire to the signal line and connect the shielding to ground.

#### Single-ended Input Connection (Shield Cable)

\*1 the AIO-160802LI-PE has eight channels.

#### **↑** CAUTION

If the signal source contains over 1MHz signals, the signal may effect the cross-talk noise between channels.

If the board and the signal source receive noise or the distance between the board and the signal source is too long, data may not be input properly.

An input analog signal should not exceed the maximum input voltage (relate to the board analog ground). If it exceeds the maximum voltage, the board may be damaged.

Connect all the unused analog input channels to analog ground.

The signal connected to an input pin may fluctuate after switching of the multiplexer. If this occurs, shorten the cable between the signal source and the analog input pin or insert a high-speed amplifier as a buffer between the two to reduce the fluctuation.

An input pin may fail to obtain input data normally when the signal source connected to the pin has high impedance. If this is the case, change the signal source to one with lower output impedance or insert a high-speed amplifier buffer between the signal source and the analog input pin to reduce the effect.

### **Analog Output Signal Connection**

This section shows how to connect the analog output signal by using a flat cable or a shielded cable.

The following figure shows an example of flat cable connection. Connect the signal source and ground to the CN1 analog output.

### **Analog Output Connection (Flat Cable)**

The following figure shows an example of shield cable connection. Use shielded cable if the distance between the signal source and board is long or if you want to provide better protection from noise. For each analog input channel on CN1, connect the core wire to the signal line and connect the shielding to ground.

#### **Analog Output Connection (Shield Cable)**

\*2 The AIO-160802LI-PE has two channels.

### ⚠ CAUTION

If the board or the connected wire receives noise, or the distance between the board and the target is long, data may not be outputted properly.

Do not short the analog output signal to analog ground, digital ground, and/or power line. Doing so may damage the board.

Do not connect an analog output signal to any other analog output, either on the board or on an external device, as this may cause a fault on the board.

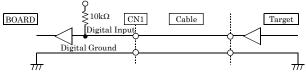

# Digital I/O signals, Counter signals and Control signals Connection

The following sections show examples of how to connect digital I/O signals, counter I/O signals, and other control I/O signals (external trigger input signals, sampling clock input signals, etc.). All the digital I/O signals and control signals are TTL level signals.

#### **Digital Input Connection**

## **Digital Output Connection**

#### About the counter input control signal

Counter Gate Control Input (refer to the page 3 Connector Pin Assignment) acts as an input that validate or invalidate the input of an external clock for the counter. This function enables the control of an external clock input for the counter. The external clock for the counter is effective when input is "High", and invalid when input is "Low". If unconnected, it is a pull-up in the board (card) and remains "High". Therefore the external clock for the counter is effective when the counter gate control input is not connected.

## ⚠ CAUTION

Do not short the output signals to analog ground, digital ground, and/or power line. Doing so may damage the board.

Do not connect a digital output signal to any other digital output, either on the board or on an external device, as this may cause a fault on the board.

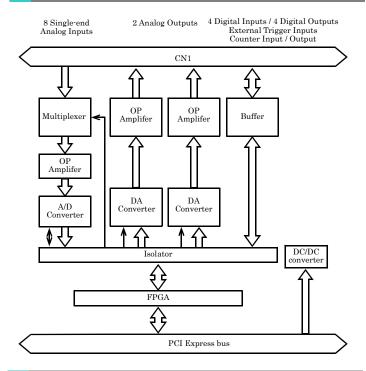

## **Block Diagram**

## Difference from ADAI16-8/2(LPCI)L

The functions same with conventional product of ADAI16-8/2(LPCI)L are provided with the AIO-160802LI-PE. In addition, as there is compatibility in terms of connector shape and pin assignments, it is easy to migrate from the existing system. So you can use the same operating procedures as ADAI16-8/2(LPCI)L.

There are some differences in specifications as shown below.

|                   | AIO-160802LI-PE       | ADAI16-8/2(LPCI)L                                      |  |  |

|-------------------|-----------------------|--------------------------------------------------------|--|--|

| Power consumption | +3.3VDC 820mA (Max.)  | +5VDC 680mA (Max.)                                     |  |  |

|                   |                       | PCI (32-bit, 33MHz,<br>Universal key shapes supported) |  |  |

| Dimension (mm)    | 169.33(L) x 110.18(H) | 121.69(L)×63.41(H)                                     |  |  |

| Weight            | 120g                  | 65g                                                    |  |  |