### DATA SHEET

### SILICONDRIVE SECURE CF **SSD-Cxxx(I)-3150**

### **OVERVIEW**

SiliconDrive Secure combines all the high performance, high reliability, and multiyear benefits lifecycle of the standard SiliconDrive Secure with a comprehensive suite of patented and patent-pending technologies that provide multiple security options to safeguard application data and software IP in embedded systems.

Applications requiring advanced levels of security such as data recorders, wearable and field computers, medical monitoring and diagnostic equipment, POS systems, and voting machines are able to activate security options to protect application data and software IP from theft, falling into the wrong hands from deployments in highrisk areas, corruption, and accidental or malicious overwrites.

### SILICONDRIVE SECURE TECHNOLOGY

PowerArmor Eliminates drive corruption

**SISMART** Calculates remaining useful

life

Ties SiliconDrive Secure to a specific host and/or software IP SiKev

SiZone Data zones with different

security parameters

SiSweep Ultra-fast data erasure

SiPurge Non-recoverable data erasure SiProtect Software write protection for

read-only access

SiSecure Password required for read/

write access

SiliconDrive Secure includes the SiliconSystems' proprietary base technologies PowerArmor and SiSMART, which eliminate drive corruption and calculate remaining useful life.

### **FEATURES**

- Integrated PowerArmor and SiSMART technology

- Capacity range: 32MB to 8GB

- Supports both 8-bit and 16-bit data register transfers

- Supports dual-voltage 3.3V or 5V interface

- Data reliability < 1 error in 10<sup>14</sup> bits read

- MTBF > 4,000,000 hours

- ATA-3 compliant

- Industry standard Type I CF form factor

- RoHS 5 of 6 compliant

- Supports PIO modes 0-4 and DMA modes 0-2

SILICONSYSTEMS PROPRIETARY

This document and the information contained within it is confidential and proprietary to SiliconSystems, Inc. All unauthorized use and/or reproduction is prohibited.

26940 ALISO VIEJO PARKWAY, ALISO VIEJO, CA 92656 • PHONE: 949.900.9400 • FAX: 949.900.9500 • http://www.siliconsystems.com

DOCUMENT: SSDS04-3150C-R MAY 22, 2007

### **REVISION HISTORY**

| Document No.                   | Release Date                 | Changes                                                                                                                                                                   |

|--------------------------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SSDS04-3150C-R                 | May 22, 2007                 | <ul> <li>Updated:</li> <li>"SiliconDrive Secure Technology."</li> <li>Removed:</li> <li>NOP command from the "ATA Command Set" table.</li> </ul>                          |

| SSDS03-3150C-R                 | February 7, 2007             | <ul> <li>Updated:</li> <li>V<sub>IH</sub> symbol from 2.0 to 2.5 in the "DC Characteristics" table.</li> <li>"Common Memory Description and Operation" tables.</li> </ul> |

| SSDS02-3150C-R                 | December 29, 2006            | <ul><li>Updated:</li><li>-CS0, -CS1 signals in the "Signal Description" table.</li></ul>                                                                                  |

| SSDS01-3150C-R  SSDS00-3150C-R | July 6, 2006<br>June 8, 2006 | Updated: • Temperature in "Environmental Specifications" table Initial release.                                                                                           |

| 33D300-3130C-IX                | Julie 0, 2000                | ililiai lelease.                                                                                                                                                          |

PAGE II MAY 22, 2007 DOCUMENT: SSDS04-3150C-R

### **TABLE OF CONTENTS**

| Overview                                        | i  |

|-------------------------------------------------|----|

| SiliconDrive Secure Technology                  | i  |

| Physical Specifications                         | 1  |

| Physical Dimensions                             | 1  |

| Product Specifications                          | 2  |

| System Performance                              | 2  |

| System Power Requirements                       | 2  |

| System Reliability                              | 2  |

| Product Capacity Specifications                 | 3  |

| Environmental Specifications                    | 3  |

| Electrical Specification                        | 4  |

| Pin Assignments                                 | 4  |

| Signal Descriptions                             | 5  |

| Absolute Maximum Ratings                        | 15 |

| Vcc = 3.3 ± 10%                                 | 15 |

| Vcc = 5.0 ± 10%                                 | 15 |

| Capacitance                                     | 15 |

| DC Characteristics                              | 16 |

| AC Characteristics                              | 17 |

| Attribute and Common Memory Read Timing         | 17 |

| Attribute and Common Memory Write Timing        | 18 |

| I/O Access Read Timing                          | 19 |

| I/O Access Write Timing                         | 20 |

| True IDE Read/Write Access Timing               | 21 |

| True IDE Multiword DMA Read/Write Access Timing | 22 |

| Attribute Memory Description and Operation      | 23 |

| Attribute Memory Read Operations                | 23 |

### SILICONSYSTEMS PROPRIETARY

This document and the information contained within it is confidential and proprietary to SiliconSystems, Inc. All unauthorized use and/or reproduction is prohibited.

|    | Attribute Memory Write Operations                  | . 24 |

|----|----------------------------------------------------|------|

|    | Attribute Memory Map                               | . 25 |

|    | Card Information Structure                         | 26   |

|    | Configuration Option Register (200h)               | 37   |

|    | Configuration and Status Register (202h)           | 38   |

|    | Pin Placement Register (204h)                      | 39   |

|    | Socket and Copy Register (206h)                    | 40   |

| C  | common Memory Description and Operation            | . 41 |

|    | Common Memory Read Operations                      | 41   |

|    | Common Memory Write Operations                     | 41   |

| I/ | O Space Description and Operation                  | . 42 |

|    | I/O Space Read Operations                          | 42   |

|    | I/O Space Write Operations                         | 42   |

| Α  | TA and True IDE Register Decoding                  | 43   |

|    | Memory-Mapped Register Decoding                    | 43   |

|    | Independent I/O Mode Register Decoding             | 44   |

|    | Primary and Secondary I/O Mapped Register Decoding | 45   |

|    | Task File Register Specification                   | 46   |

| Δ  | TA Registers                                       | . 47 |

|    | Data Register                                      | . 47 |

|    | Error Register                                     | 47   |

|    | Feature Register                                   | 48   |

|    | Sector Count Register                              | 49   |

|    | Sector Number Register                             | 50   |

|    | Cylinder Low Register                              | 51   |

|    | Cylinder High Register                             | . 52 |

|    | Drive/Head Register                                | 53   |

|    | Status Register                                    |      |

|    | Command Register                                   | . 55 |

|   | Alternate Status Register             | 56 |

|---|---------------------------------------|----|

|   | Device Control Register               | 57 |

|   | Device Address Register               | 58 |

| A | ATA Command Block and Set Description | 59 |

|   | ATA Command Set                       | 59 |

|   | Check Power Mode — 98h, E5h           | 61 |

|   | Executive Drive Diagnostic — 90h      | 62 |

|   | Format Track — 50h                    | 63 |

|   | Identify Drive — ECh                  | 64 |

|   | Identify Drive — Drive Attribute Data | 65 |

|   | Idle — 97h, E3h                       | 68 |

|   | Idle Immediate — 95h, E1h             | 69 |

|   | Initialize Drive Parameters — 91h     | 70 |

|   | Recalibrate — 1Xh                     | 71 |

|   | Read Buffer — E4h                     | 72 |

|   | Read DMA — C8h                        | 73 |

|   | Read Multiple — C4h                   | 74 |

|   | Read Sector — 20h, 21h                | 75 |

|   | Read Long Sector(s) — 22h, 23h        | 76 |

|   | Read Verify Sector(s) — 40h, 41h      | 77 |

|   | Seek — 7Xh                            | 78 |

|   | Set Features — EFh                    | 79 |

|   | Set Multiple Mode — C6h               | 80 |

|   | Set Sleep Mode — 99h, E6h             | 81 |

|   | Standby — 96h, E2h                    | 82 |

|   | Standby Immediate — 94h, E0h          | 83 |

|   | Write Buffer — E8h                    | 84 |

|   | Write DMA — CAh                       | 85 |

|   | Write Multiple — C5h                  | 86 |

This document and the information contained within it is confidential and proprietary to SiliconSystems, Inc. All unauthorized use and/or reproduction is prohibited.

|        | Write Sector(s) — 30h, 31h      | 87 |

|--------|---------------------------------|----|

|        | Write Long Sector(s) — 32h, 33h | 88 |

|        | Erase Sector(s) — C0h           | 89 |

|        | Request Sense — 03h             | 90 |

|        | Translate Sector — 87h          | 91 |

|        | Wear-Level — F5h                | 92 |

|        | Write Multiple w/o Erase — CDh  | 93 |

|        | Write Sector(s) w/o Erase — 38h | 94 |

|        | Write Verify — 3Ch              | 95 |

| Sales  | and Support                     | 96 |

| Part I | Numbering                       | 96 |

| Nor    | menclature                      | 96 |

| Par    | t Numbers                       | 97 |

| Sar    | nple Label                      | 97 |

| Relat  | ed Documentation                | 98 |

### **LIST OF FIGURES**

| Figure 1: Physical Dimensions                              | 1  |

|------------------------------------------------------------|----|

| Figure 2: Attribute and Common Memory Read Timing Diagram  | 17 |

| Figure 3: Attribute and Common Memory Write Timing Diagram | 18 |

| Figure 4: I/O Access Read Timing Diagram                   | 19 |

| Figure 5: I/O Access Write Timing Diagram                  | 20 |

| Figure 6: True IDE Read/Write Access Timing Diagram        | 21 |

| Figure 7: True IDE Multiword DMA Read/Write Access Timing  | 22 |

| Figure 8: Sample Label                                     | 97 |

### SILICONSYSTEMS PROPRIETARY

This document and the information contained within it is confidential and proprietary to SiliconSystems, Inc. All unauthorized use and/or reproduction is prohibited.

This document and the information contained within it is confidential and proprietary to SiliconSystems, Inc. All unauthorized use and/or reproduction is prohibited.

PAGE VIII MAY 22, 2007 DOCUMENT: SSDS04-3150C-R

### **LIST OF TABLES**

| Table 1: System Performance                               | 2  |

|-----------------------------------------------------------|----|

| Table 2: System Power Requirements                        | 2  |

| Table 3: System Reliability                               | 2  |

| Table 4: Product Capacity Specifications                  | 3  |

| Table 5: Environmental Specifications                     | 3  |

| Table 6: Pin Assignments                                  | 4  |

| Table 7: Signal Descriptions                              | 5  |

| Table 8: Absolute Maximum Rating — Vcc = 3.3 ± 10%        | 15 |

| Table 9: Absolute Maximum Rating — Vcc = 5.0 ± 10%        | 15 |

| Table 10: Capacitance                                     | 15 |

| Table 11: DC Characteristics                              | 16 |

| Table 12: Attribute and Common Memory Read Timing         | 17 |

| Table 13: Attribute and Common Memory Write Timing        | 18 |

| Table 14: I/O Access Read Timing                          | 19 |

| Table 15: I/O Access Write Timing                         |    |

| Table 16: True IDE Read/Write Access Timing               | 21 |

| Table 17: True IDE Multiword DMA Read/Write Access Timing | 22 |

| Table 18: Attribute Memory Read Operations                | 23 |

| Table 19: Attribute Memory Write Operations               | 24 |

| Table 20: Attribute Memory Map                            | 25 |

| Table 21: Card Information Structure                      | 26 |

| Table 22: Configuration Option Register (200h)            | 37 |

| Table 23: Configuration and Status Register (202h)        | 38 |

| Table 24: Pin Placement Register (204h)                   | 39 |

| Table 25: Socket and Copy Register (206h)                 | 40 |

| Table 26: Common Memory Read Operations                   | 41 |

| Table 27: Common Memory Write Operations                  | 41 |

### SILICONSYSTEMS PROPRIETARY

This document and the information contained within it is confidential and proprietary to SiliconSystems, Inc. All unauthorized use and/or reproduction is prohibited.

| Table 28: I/O Space Read Operations                          | 42 |

|--------------------------------------------------------------|----|

| Table 29: I/O Space Write Operations                         | 42 |

| Table 30: Memory-Mapped Register Decoding                    | 43 |

| Table 31: Independent I/O Mode Register Decoding             | 44 |

| Table 32: Primary and Secondary I/O Mapped Register Decoding | 45 |

| Table 33: Task File Register Specification                   | 46 |

| Table 34: Error Register                                     | 47 |

| Table 35: Feature Register                                   | 48 |

| Table 36: Sector Count Register                              | 49 |

| Table 37: Sector Number Register                             | 50 |

| Table 38: Cylinder Low Register                              | 51 |

| Table 39: Cylinder High Register                             | 52 |

| Table 40: Drive/Head Register                                | 53 |

| Table 41: Status Register                                    | 54 |

| Table 42: Command Register                                   | 55 |

| Table 43: Alternate Status Register                          | 56 |

| Table 44: Device Control Register                            | 57 |

| Table 45: Device Address Register                            | 58 |

| Table 46: ATA Command Block and Set Description              | 59 |

| Table 47: ATA Command Set                                    | 59 |

| Table 48: Check Power Mode — 98h, E5h                        | 61 |

| Table 49: Executive Drive Diagnostic — 90h                   | 62 |

| Table 50: Format Track — 50h                                 | 63 |

| Table 51: Identify Drive — ECh                               | 64 |

| Table 52: Identify Drive — Drive Attribute Data              | 65 |

| Table 53: Idle — 97h, E3h                                    | 68 |

| Table 54: Idle Immediate — 95h, E1h                          | 69 |

| Table 55: Initialize Drive Parameters — 91h                  | 70 |

| Table 56: Recalibrate — 1Yh                                  | 71 |

| Table 57: Read  | d Buffer — E4h                | 72 |

|-----------------|-------------------------------|----|

| Table 58: Read  | d DMA — C8h                   | 73 |

| Table 59: Read  | d Multiple — C4h              | 74 |

| Table 60: Read  | d Sector — 20h, 21h           | 75 |

| Table 61: Read  | d Long Sector(s) — 22h, 23h   | 76 |

| Table 62: Read  | d Verify Sector(s) — 40h, 41h | 77 |

| Table 63: Seek  | < — 7Xh                       | 78 |

| Table 64: Set F | Features — EFh                | 79 |

| Table 65: Set F | Features' Attributes          | 79 |

| Table 66: Set N | Multiple Mode — C6h           | 80 |

| Table 67: Set S | Sleep Mode — 99h, E6h         | 81 |

| Table 68: Stan  | ldby — 96h, E2h               | 82 |

| Table 69: Stan  | dby Immediate — 94h, E0h      | 83 |

| Table 70: Write | e Buffer — E8h                | 84 |

| Table 71: Write | e DMA — CAh                   | 85 |

| Table 72: Write | e Multiple — C5h              | 86 |

| Table 73: Write | e Sector(s) — 30h, 31h        | 87 |

| Table 74: Write | e Long Sector(s) — 32h, 33h   | 88 |

| Table 75: Eras  | se Sector(s) — C0h            | 89 |

| Table 76: Requ  | uest Sense — 03h              | 90 |

| Table 77: Exte  | nded Error Codes              | 90 |

| Table 78: Tran  | slate Sector — 87h            | 91 |

| Table 79: Wea   | r-Level — F5h                 | 92 |

| Table 80: Write | e Multiple w/o Erase — CDh    | 93 |

| Table 81: Write | e Sector(s) w/o Erase — 38h   | 94 |

| Table 82: Write | e Verify — 3Ch                | 95 |

| Table 83: Part  | Numbering Nomenclature        | 96 |

| Table 84: Part  | Numbers                       | 97 |

| Table 85: Rela  | ted Documentation             | 98 |

This document and the information contained within it is confidential and proprietary to SiliconSystems, Inc. All unauthorized use and/or reproduction is prohibited.

This document and the information contained within it is confidential and proprietary to SiliconSystems, Inc. All unauthorized use and/or reproduction is prohibited.

PAGE XII MAY 22, 2007 DOCUMENT: SSDS04-3150C-R

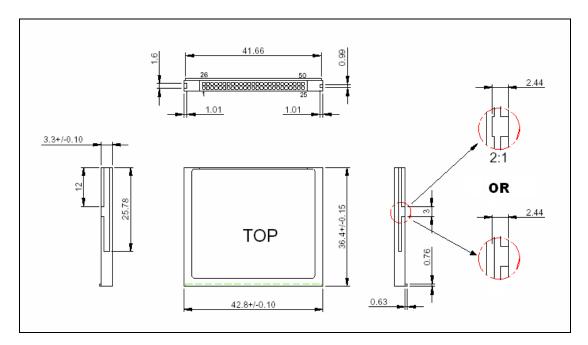

### PHYSICAL SPECIFICATIONS

The SiliconDrive Secure CF products are offered in an industry-standard Type I form factor. See "Part Numbering" on page 96 for details regarding CF capacities.

### PHYSICAL DIMENSIONS

This section provides diagrams that describe the physical dimensions for the CF.

Figure 1: Physical Dimensions

### SILICONSYSTEMS PROPRIETARY

This document and the information contained within it is confidential and proprietary to SiliconSystems, Inc.

All unauthorized use and/or reproduction is prohibited.

### **PRODUCT SPECIFICATIONS**

**Note:** All SiliconDrive Secure CF values quoted are typical at 25°C and nominal supply voltage.

### SYSTEM PERFORMANCE

Table 1: System Performance

| Reset to Ready Startup Time (Typical/Max) | 200ms/400ms |

|-------------------------------------------|-------------|

| Read Transfer Rate (Typical)              | 8MBps       |

| Write Transfer Rate (Typical)             | 6MBps       |

| Burst Transfer Rate                       | 16.7MBps    |

| Controller Overhead (Command to DRQ)      | 2ms (max)   |

### SYSTEM POWER REQUIREMENTS

Table 2: System Power Requirements

| DC Input Voltage        | 3.3 ± 10% | 5.0 ± 10%  |

|-------------------------|-----------|------------|

| Sleep (Standby Current) | <0.5mA    | <1.0mA     |

| Read (Typical/Peak)     | 20mA/75mA | 30mA/100mA |

| Write (Typical/Peak)    | 30mA/75mA | 40mA/100mA |

### SYSTEM RELIABILITY

Table 3: System Reliability

| MTBF (@ 25°C)    | > 4,000,000 hours                                       |

|------------------|---------------------------------------------------------|

| Data Reliability | < 1 non-recoverable error in 10 <sup>14</sup> bits read |

| Endurance        | >2,000,000 write/erase cycles                           |

| Data Retention   | 10 years                                                |

### SILICONSYSTEMS PROPRIETARY

This document and the information contained within it is confidential and proprietary to SiliconSystems, Inc.

All unauthorized use and/or reproduction is prohibited.

PAGE 2 MAY 22, 2007 DOCUMENT: SSDS04-3150C-R

### **PRODUCT CAPACITY SPECIFICATIONS**

Table 4: Product Capacity Specifications

| Product<br>Capacity | Formatted<br>Capacity<br>(Bytes) | Number of<br>Sectors | Number of Cylinders | Number of Heads | Number of<br>Sectors/<br>Track |

|---------------------|----------------------------------|----------------------|---------------------|-----------------|--------------------------------|

| 32MB                | 32,702,464                       | 63,872               | 499                 | 4               | 32                             |

| 64MB                | 65,601,536                       | 128,128              | 1001                | 4               | 32                             |

| 128MB               | 130,154,496                      | 254,208              | 993                 | 8               | 32                             |

| 256MB               | 260,571,136                      | 508,928              | 994                 | 16              | 32                             |

| 512MB               | 521,773,056                      | 1,019,088            | 1011                | 16              | 63                             |

| 1GB                 | 1,047,674,880                    | 2,046,240            | 2030                | 16              | 63                             |

| 2GB                 | 2,098,446,336                    | 4,098,528            | 4066                | 16              | 63                             |

| 4GB                 | 4,224,761,856                    | 8,251,488            | 8186                | 16              | 63                             |

| 8GB                 | 8,455,200,768                    | 16,514,064           | 16,383*             | 16              | 63                             |

<sup>\* =</sup> All IDE drives 8GB and larger use 16383 cylinders, 16 heads, and 63 sectors/track due to interface restrictions.

### **ENVIRONMENTAL SPECIFICATIONS**

Table 5: Environmental Specifications

| 0°C to 70°C (Commercial)                                       |

|----------------------------------------------------------------|

| -40°C to 85°C (Industrial)                                     |

| 8% to 95% non-condensing                                       |

| 16.3gRMS, MIL-STD-810F, Method 514.5, Procedure I, Category 24 |

| 1000G, Half-sine, 0.5ms Duration                               |

| 50g Pk, MIL-STD-810F, Method 516.5, Procedure I                |

| 80,000ft, MIL-STD-810F, Method 500.4, Procedure II             |

|                                                                |

### SILICONSYSTEMS PROPRIETARY

This document and the information contained within it is confidential and proprietary to SiliconSystems, Inc.

All unauthorized use and/or reproduction is prohibited.

### **ELECTRICAL SPECIFICATION**

### **PIN ASSIGNMENTS**

The following table describes the SiliconDrive Secure CF 50-pin IDE connector signals.

Table 6: Pin Assignments

| Pin | PC Card<br>Memory<br>Mode | PC Card<br>I/O Mode | IDE-ATA<br>Mode |

|-----|---------------------------|---------------------|-----------------|

| 1   | GND                       | GND                 | GND             |

| 2   | D3                        | D3                  | D3              |

| 3   | D4                        | D4                  | D4              |

| 4   | D5                        | D5                  | D5              |

| 5   | D6                        | D6                  | D6              |

| 6   | D7                        | D7                  | D7              |

| 7   | CE1#                      | CE1#                | CE1#            |

| 8   | A10                       | A10                 | A10             |

| 9   | OE#                       | OE#                 | OE#             |

| 10  | A9                        | A9                  | A9 <sup>2</sup> |

| 11  | A8                        | A8                  | A8 <sup>2</sup> |

| 12  | A7                        | A7                  | A7 <sup>2</sup> |

| 13  | VCC                       | VCC                 | VCC             |

| 14  | A6                        | A6                  | A6 <sup>2</sup> |

| 15  | A5                        | A5                  | A5 <sup>2</sup> |

| 16  | A4                        | A4                  | A4 <sup>2</sup> |

| 17  | A3                        | A3                  | A3 <sup>2</sup> |

| 18  | A2                        | A2                  | A2              |

| 19  | A1                        | A1                  | A1              |

| 20  | A0                        | A0                  | A0              |

| 21  | D0                        | D0                  | D0              |

| 22  | D1                        | D1                  | D1              |

| 23  | D2                        | D2                  | D2              |

| 24  | WP                        | -IOIS16             | -IOIS16         |

| 25  | CD2#                      | CD2#                | CD2#            |

| Pin | PC Card<br>Memory<br>Mode | PC Card<br>I/O Mode | IDE-ATA<br>Mode  |

|-----|---------------------------|---------------------|------------------|

| 26  | CD1#                      | CD1#                | CD1#             |

| 27  | D11 <sup>1</sup>          | D11 <sup>1</sup>    | D11 <sup>1</sup> |

| 28  | D12 <sup>1</sup>          | D12 <sup>1</sup>    | D12 <sup>1</sup> |

| 29  | D13 <sup>1</sup>          | D13 <sup>1</sup>    | D13 <sup>1</sup> |

| 30  | D14 <sup>1</sup>          | D14 <sup>1</sup>    | D14 <sup>1</sup> |

| 31  | D15 <sup>1</sup>          | D15 <sup>1</sup>    | D15 <sup>1</sup> |

| 32  | CE2#                      | CE2#                | CE2#             |

| 33  | VS1#                      | VS1#                | VS1#             |

| 34  | IORD#                     | IORD#               | IORD#            |

| 35  | IOWR#                     | IOWR#               | IOWR#            |

| 36  | WE#                       | WE#                 | WE#              |

| 37  | RDY/BSY                   | IREQ                | RDY/BSY          |

| 38  | VCC                       | VCC                 | VCC              |

| 39  | CSEL#                     | CSEL#               | CSEL#            |

| 40  | VS2#                      | VS2#                | VS2#             |

| 41  | RESET#                    | RESET#              | RESET#           |

| 42  | WAIT#                     | WAIT#               | WAIT#            |

| 43  | INPACK#                   | INPACK#             | DMARQ            |

| 44  | REG#                      | REG#                | DMACK#           |

| 45  | BVD2                      | SPKR#               | DASP#            |

| 46  | BVD1                      | STSCHG#             | PDIAG#           |

| 47  | D8 <sup>1</sup>           | D8 <sup>1</sup>     | D8 <sup>1</sup>  |

| 48  | D9 <sup>1</sup>           | D9 <sup>1</sup>     | D9 <sup>1</sup>  |

| 49  | D10 <sup>1</sup>          | D10 <sup>1</sup>    | D10 <sup>1</sup> |

| 50  | GND                       | GND                 | GND              |

### Notes:

- 1 = These signals are required only for 16-bit access, and not required when installed in 8-bit systems.

- 2 = Should be grounded by the host.

### SILICONSYSTEMS PROPRIETARY

This document and the information contained within it is confidential and proprietary to SiliconSystems, Inc.

All unauthorized use and/or reproduction is prohibited.

PAGE 4 MAY 22, 2007 DOCUMENT: SSDS04-3150C-R

### SIGNAL DESCRIPTIONS

Table 7: Signal Descriptions

| Signal Name                      | Pin                                      | Туре | Description                                                                                                                                                                                                                                                                     |

|----------------------------------|------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A10-A0                           | 8, 10, 11,<br>12, 14, 15,<br>16, 17, 18, | I    | These address lines along with the - REG signal are used to select the following:                                                                                                                                                                                               |

|                                  | 19, 20                                   |      | <ul> <li>The I/O port address registers within the SiliconDrive Secure CF</li> <li>The memory-mapped port address registers within the SiliconDrive Secure CF</li> <li>A byte in the card's information structure and its configuration control and status registers</li> </ul> |

| A10-A0<br>(PC Card I/O<br>mode)  |                                          |      | This signal is the same as the PC Card Memory Mode signal.                                                                                                                                                                                                                      |

| A2-A0<br>(True IDE mode)         | 18, 19, 20                               | I    | In true IDE mode, only A[2:0] are used to select the one of eight registers in the Task File. The remaining address lines should be grounded by the host.                                                                                                                       |

| BVD1<br>(PC Card memory<br>mode) | 46                                       | I/O  | This signal is asserted high, because BVD1 is not supported.                                                                                                                                                                                                                    |

| -STSCHG<br>(PC Card I/O<br>mode) |                                          |      | This signal is asserted low to alert the host to changes in the RDY/-BSY and Write Protect states while the I/O interface is configured. This signal's use is controlled by the Card Configuration and Status register.                                                         |

| -PDIAG<br>(True IDE mode)        |                                          |      | In the true IDE mode, this input/<br>output is the Pass Diagnostic signal in<br>the Master/Slave handshake protocol.                                                                                                                                                            |

### SILICONSYSTEMS PROPRIETARY

This document and the information contained within it is confidential and proprietary to SiliconSystems, Inc.

All unauthorized use and/or reproduction is prohibited.

Table 7: Signal Descriptions (Continued)

| Signal Name                            | Pin    | Туре | Description                                                                                                                                                                            |

|----------------------------------------|--------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BVD2<br>(PC Card memory<br>mode)       | 45     | I/O  | This signal is asserted high, as BVD2 is not supported.                                                                                                                                |

| -SPKR<br>(PC Card I/O<br>mode)         |        |      | This line is the Binary Audio output from the card. If the Card does not support the Binary Audio function, this line should be held negated.                                          |

| -DASP<br>(True IDE mode)               |        |      | In the true IDE mode, this input/output is the Disk Active/Slave Present signal in the Master/Slave handshake protocol.                                                                |

| -CD1, -CD2<br>(PC Card memory<br>mode) | 26, 25 | 0    | These Card Detect pins are connected to ground on the SiliconDrive Secure CF, and are used by the host to determine that the SiliconDrive Secure CF is fully inserted into its socket. |

| -CD1, -CD2<br>(PC Card I/O<br>Mode)    |        |      | This signal is the same for all modes.                                                                                                                                                 |

| -CD1, -CD2<br>(True IDE mode)          |        |      | This signal is the same for all modes.                                                                                                                                                 |

PAGE 6 MAY 22, 2007 DOCUMENT: SSDS04-3150C-R

Table 7: Signal Descriptions (Continued)

| Signal Name                                           | Pin   | Туре | Description                                                                                                                                                                                                                                                                                       |

|-------------------------------------------------------|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -CE1, -CE2<br>(PC Card memory<br>mode)<br>Card Enable | 7, 32 | I    | These input signals are used both to select the card and to indicate to the card whether a byte or a word operation is being performed.                                                                                                                                                           |

|                                                       |       |      | <ul> <li>-CE2 always accesses the odd<br/>byte of the word.</li> <li>-CE1 accesses the even byte or<br/>the odd byte of the word depending<br/>on A0 and -CE2.</li> </ul>                                                                                                                         |

|                                                       |       |      | A multiplexing scheme based on A0, -CE1, and -CE2 allows 8-bit hosts to access all data on D0-D7. See "Attribute Memory Read Operations" on page 23, "Attribute Memory Write Operations" on page 24, "Common Memory Read Operations" on page 41, and "Common Memory Write Operations" on page 41. |

| -CE1, -CE2<br>(PC Card I/O<br>mode)<br>Card Enable    |       |      | This signal is the same as the PC Card Memory Mode signal. See "I/O Space Read Operations" on page 42 and "I/O Space Write Operations" on page 42.                                                                                                                                                |

| -CS0, -CS1<br>(True IDE mode)                         |       |      | In the true IDE mode, -CS0 is the chip select for the task file registers while -CS1 is used to select the Alternate Status register and the Device Control register.                                                                                                                             |

This document and the information contained within it is confidential and proprietary to SiliconSystems, Inc.

All unauthorized use and/or reproduction is prohibited.

Table 7: Signal Descriptions (Continued)

| Signal Name                                           | Pin | Туре | Description                                                                                                                                                                                                                                                                                      |

|-------------------------------------------------------|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -CSEL<br>(PC Card memory<br>mode)                     | 39  | I    | This signal is not used for this mode.                                                                                                                                                                                                                                                           |

| -CSEL<br>(PC Card I/O<br>mode)                        |     |      | This signal is not used for this mode.                                                                                                                                                                                                                                                           |

| -CSEL<br>(True IDE mode)                              |     |      | This internally pulled-up signal is used to configure this device as a master or slave when configured in the true IDE mode. When this pin is:                                                                                                                                                   |

|                                                       |     |      | <ul> <li>Grounded, this device is configured as a master.</li> <li>Open, this device is configured as a slave.</li> </ul>                                                                                                                                                                        |

| -INPACK<br>(PC Card memory<br>mode)                   | 43  | 0    | This signal is not used in this mode.                                                                                                                                                                                                                                                            |

| -INPACK<br>(PC Card I/O<br>mode)<br>Input Acknowledge |     |      | This signal is asserted by the SiliconDrive Secure CF when the card is selected and responding to an I/O read cycle at the address that is on the address bus. This signal is used by the host to control the enabling of any input data buffers between the SiliconDrive Secure CF and the CPU. |

PAGE 8 MAY 22, 2007 DOCUMENT: SSDS04-3150C-R

Table 7: Signal Descriptions (Continued)

| Signal Name                         | Pin                                                                   | Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------------------------|-----------------------------------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DMARQ<br>(True IDE mode)            | 43                                                                    | 0    | In true IDE mode, this signal is used for DMA transfers between the host and device. DMARQ is asserted by the device when the device is ready to transfer data to/from the host. The direction of data transfer is controlled by -IORD and -IOWR. This signal is used in a handshake manner with -DMACK (i.e., the device waits until the host asserts -DMACK before negating DMARQ, and reasserts DMARQ if there is more data to transfer). The DMARQ/-DMACK handshake is used to provide flow control during the transfer. |

| D15-D00<br>(PC Card memory<br>mode) | 31, 30, 29,<br>28, 27, 49,<br>48, 47, 6,<br>5, 4, 3, 2,<br>23, 22, 21 | I/O  | <ul> <li>These lines carry the data, commands, and status information between the host and the controller.</li> <li>D00 is the LSB of the word's even byte.</li> <li>D08 is the LSB of the word's odd byte.</li> </ul>                                                                                                                                                                                                                                                                                                       |

| D15-D00<br>(PC Card I/O<br>mode)    |                                                                       |      | This signal is the same as the PC Card Memory Mode signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| D15-D00<br>(True IDE mode)          |                                                                       |      | In true IDE mode, all Task File operations occur in byte mode on the low-order bus D00-D07, while all data transfers are 16 bits using D00-D15.                                                                                                                                                                                                                                                                                                                                                                              |

| GND<br>(PC Card memory<br>mode)     | 1, 50                                                                 | -    | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| GND<br>(PC Card I/O<br>mode)        |                                                                       |      | This signal is the same for all modes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| GND<br>(True IDE mode)              |                                                                       |      | This signal is the same for all modes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| (TIGO IDE MOGO)                     |                                                                       |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

This document and the information contained within it is confidential and proprietary to SiliconSystems, Inc.

All unauthorized use and/or reproduction is prohibited.

Table 7: Signal Descriptions (Continued)

| Signal Name                       | Pin | Туре | Description                                                                                                                                                                                            |

|-----------------------------------|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -IORD<br>(PC Card memory<br>mode) | 34  | I    | This signal is not used in this mode.                                                                                                                                                                  |

| -IORD<br>(PC Card I/O<br>mode)    |     |      | This is an I/O read strobe generated by the host. This signal gates I/O data onto the bus from the SiliconDrive Secure CF when the card is configured to use the I/O interface.                        |

| -IORD<br>(True IDE mode)          |     |      | In true IDE mode, this signal has the same function as the PC Card I/O mode.                                                                                                                           |

| -IOWR<br>(PC Card memory<br>mode) | 35  | I    | This signal is not used in this mode.                                                                                                                                                                  |

| -IOWR<br>(PC Card I/O<br>mode)    |     |      | The I/O write strobe pulse is used to clock I/O data on the Card data bus into the SiliconDrive Secure CF controller registers when the SiliconDrive Secure CF is configured to use the I/O interface. |

|                                   |     |      | The clocking occurs on the negative-to-positive edge of the signal (the trailing edge).                                                                                                                |

| -IOWR<br>(True IDE mode)          |     |      | In true IDE mode, this signal has the same function as the PC Card I/O mode.                                                                                                                           |

| -OE<br>(PC Card memory<br>mode)   | 9   | I    | This is an output enable strobe generated by the host interface, which is used to read:                                                                                                                |

|                                   |     |      | <ul> <li>Data from the SiliconDrive Secure<br/>CF in memory mode.</li> <li>The CIS and configuration<br/>registers.</li> </ul>                                                                         |

| -OE<br>(PC Card I/O<br>mode)      |     |      | In PC Card I/O mode, this signal is used to read the CIS and configuration registers.                                                                                                                  |

This document and the information contained within it is confidential and proprietary to SiliconSystems, Inc.

All unauthorized use and/or reproduction is prohibited.

Table 7: Signal Descriptions (Continued)

| Signal Name                                         | Pin | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------------------------------------|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -ATA SEL<br>(True IDE mode)                         |     |      | To enable true IDE mode, this input should be grounded by the host.                                                                                                                                                                                                                                                                                                                                                                                                    |

| -RDY/-BSY                                           | 37  | Ο    | In memory mode, this signal is:                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| (PC Card memory mode)                               |     |      | <ul> <li>Set high when the SiliconDrive<br/>Secure CF is ready to accept a<br/>new data transfer operation.</li> <li>Held low when the card is busy.</li> </ul>                                                                                                                                                                                                                                                                                                        |

|                                                     |     |      | The host memory card socket must provide a pull-up resistor.  At power-up and reset, the RDY/-BSY signal is held low (busy) until the SiliconDrive Secure CF has completed its power-up or reset function. No access of any type should be made to the SiliconDrive Secure CF during this time. The RDY/-BSY signal is held high (disabled from being busy) whenever the SiliconDrive Secure CF has been powered up with +RESET continuously disconnected or asserted. |

| -IREQ<br>(PC Card I/O<br>mode)<br>Input Acknowledge |     |      | I/O Operation. After the SiliconDrive Secure CF has been configured for I/O operation, this signal is used as -Interrupt Request. This line is strobed low to generate a pulse mode interrupt or held low for a level mode interrupt.                                                                                                                                                                                                                                  |

| -IREQ<br>(True IDE mode)                            |     |      | In true IDE mode, this signal is the active high Interrupt Request to the host.                                                                                                                                                                                                                                                                                                                                                                                        |

This document and the information contained within it is confidential and proprietary to SiliconSystems, Inc.

All unauthorized use and/or reproduction is prohibited.

Table 7: Signal Descriptions (Continued)

| Signal Name                                                    | Pin | Туре | Description                                                                                                                                                                                                                                                                                  |

|----------------------------------------------------------------|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -REG<br>(PC Card memory<br>mode)<br>Attribute Memory<br>Select | 44  | I    | This signal is used during memory cycles to distinguish between common memory and register (attribute) memory accesses. This signal is set:                                                                                                                                                  |

|                                                                |     |      | <ul><li>High for common memory.</li><li>Low for attribute memory.</li></ul>                                                                                                                                                                                                                  |

| -REG<br>(PC Card I/O<br>mode)                                  |     |      | The signal must also be active (low) during I/O cycles when the I/O address is on the bus.                                                                                                                                                                                                   |

| -DMACK<br>(True IDE mode)                                      |     |      | In true IDE mode, this signal is used by the host in response to DMARQ to initiate DMA transfers. The DMARQ/-DMACK handshake is used to provide flow control during the transfer. When -DMACK is asserted, -CS0 and -CS1 are not asserted and transfers are 16-bits wide.                    |

| -RESET<br>(PC Card memory<br>mode)                             | 41  | I    | When the pin is high, this signal resets the SiliconDrive Secure CF. The SiliconDrive Secure CF is reset only at power-up if this pin is left high or open from power-up. The SiliconDrive Secure CF is also reset when the Soft Reset bit in the Card Configuration Option register is set. |

| -RESET<br>(PC Card I/O<br>mode)                                |     |      | This signal is the same as the PC Card Memory Mode signal.                                                                                                                                                                                                                                   |

| -RESET<br>(True IDE mode)                                      |     |      | In the true IDE mode, this input pin is the active low hardware reset from the host.                                                                                                                                                                                                         |

This document and the information contained within it is confidential and proprietary to SiliconSystems, Inc.

All unauthorized use and/or reproduction is prohibited.

Table 7: Signal Descriptions (Continued)

| Signal Name                         | Pin    | Type | Description                                                                                                                                                                |

|-------------------------------------|--------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VCC<br>(PC Card memory<br>mode)     | 13, 38 | -    | +5V, +3.3V power.                                                                                                                                                          |

| VCC<br>(PC Card I/O<br>mode)        |        |      | This signal is the same for all modes.                                                                                                                                     |

| VCC<br>(True IDE mode)              |        |      | This signal is the same for all modes.                                                                                                                                     |

| -VS1, -VS2                          | 33, 40 | 0    | Voltage Sense Signals.                                                                                                                                                     |

|                                     |        |      | <ul> <li>-VS1 is grounded so that the<br/>SiliconDrive Secure CF CIS can be<br/>read at 3.3V.</li> <li>-VS2 is reserved by PC Card for a<br/>secondary voltage.</li> </ul> |

| -VS1, -VS2<br>(PC Card I/O<br>mode) |        |      | This signal is the same for all modes.                                                                                                                                     |

| -VS1, -VS2<br>(True IDE mode)       |        |      | This signal is the same for all modes.                                                                                                                                     |

| -WAIT<br>(PC Card memory<br>mode)   | 42     | 0    | The -WAIT signal is driven low by the SiliconDrive Secure CF to signal the host to delay completion of a memory or I/O cycle that is in progress.                          |

| -WAIT<br>(PC Card I/O<br>mode)      |        |      | This signal is the same as the PC Card Memory Mode signal.                                                                                                                 |

| -IORDY<br>(True IDE mode)           |        |      | In true IDE mode, this output signal may be used as IORDY.                                                                                                                 |

This document and the information contained within it is confidential and proprietary to SiliconSystems, Inc.

All unauthorized use and/or reproduction is prohibited.

Table 7: Signal Descriptions (Continued)

| Signal Name                      | Pin | Туре | Description                                                                                                                                                                                                                                                              |

|----------------------------------|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -WE<br>(PC Card memory<br>mode)  | 36  | I    | This is a signal driven by the host and used for strobing memory write data to the registers of the SiliconDrive Secure CF when the card is configured in the memory interface mode. This signal is also used for writing the configuration registers.                   |

| -WE<br>(PC Card I/O<br>mode)     |     |      | In PC Card I/O mode, this signal is used for writing the configuration registers.                                                                                                                                                                                        |

| -WE<br>(True IDE mode)           |     |      | In true IDE mode, this input signal is not used and should be connected to VCC by the host.                                                                                                                                                                              |

| WP<br>(PC Card memory<br>mode)   | 24  | 0    | Write Protect Memory Mode. The SiliconDrive Secure CF does not have a write protect switch. This signal is held low after the completion of the reset initialization sequence.                                                                                           |

| -IOIS16<br>(PC Card I/O<br>mode) |     |      | I/O Operation. When the SiliconDrive Secure CF is configured for I/O operation, pin 24 is used for the -I/O Selected, which is a 16-bit port (-IOIS16) function. A low signal indicates that a 16-bit or odd byte only operation can be performed at the addressed port. |

| -IOIS16<br>(True IDE mode)       |     |      | In true IDE mode, this output signal is asserted low when this device is expecting a word data transfer cycle.                                                                                                                                                           |

### **ABSOLUTE MAXIMUM RATINGS**

$Vcc = 3.3 \pm 10\%$

Table 8: Absolute Maximum Rating —  $Vcc = 3.3 \pm 10\%$

| Symbol | Parameter               | Minimum | Maximum | Units |

|--------|-------------------------|---------|---------|-------|

| Ts     | Storage Temperature     | -55     | 125     | °C    |

| $T_A$  | Operating Temperature   | -40     | 85      | °C    |

| Vcc    | Vcc with Respect to GND | -0.3    | 6.7     | V     |

| Vin    | Input Voltage           | -0.5    | 3.8     | V     |

| Vout   | Output Voltage          | -0.3    | 3.6     | V     |

$Vcc = 5.0 \pm 10\%$

Table 9: Absolute Maximum Rating —  $Vcc = 5.0 \pm 10\%$

| Symbol         | Parameter               | Minimum | Maximum | Units |

|----------------|-------------------------|---------|---------|-------|

| Ts             | Storage Temperature     | -55     | 125     | °C    |

| T <sub>A</sub> | Operating Temperature   | -40     | 85      | °C    |

| Vcc            | Vcc with Respect to GND | -0.3    | 6.7     | V     |

| Vin            | Input Voltage           | -0.5    | 6.0     | V     |

| Vout           | Output Voltage          | -0.3    | 5.8     | V     |

### **CAPACITANCE**

Table 10: Capacitance

| Symbol | Parameter                 | Maximum | Units |

|--------|---------------------------|---------|-------|

| Cin    | Input Capacitance         | 35      | pF    |

| Cout   | Output Capacitance        | 35      | pF    |

| CI/O   | Bidirectional Capacitance | 35      | pF    |

### SILICONSYSTEMS PROPRIETARY

This document and the information contained within it is confidential and proprietary to SiliconSystems, Inc.

All unauthorized use and/or reproduction is prohibited.

### **DC CHARACTERISTICS**

Table 11: DC Characteristics

| Symbol           | Parameter                         | 3.3 V ±10% |          | 5V ±10% |          | Units |

|------------------|-----------------------------------|------------|----------|---------|----------|-------|

| Syllibol         | i arameter                        | Minimum    | Maximum  | Minimum | Maximum  | Omis  |

| Vcc              | Power Supply<br>Voltage           | 3.0        | 3.6      | 4.5     | 5.5      | V     |

| I <sub>LI</sub>  | Input Leakage<br>*(1) Current     | -          | 5        | -       | 5        | μA    |

| I <sub>LO</sub>  | Output<br>Leakage *(1)<br>Current | -          | 5        | -       | 5        | μA    |

| V <sub>CCR</sub> | Vcc Read<br>Current               | -          | 50       | -       | 80       | mA    |

| V <sub>CCW</sub> | Vcc Write<br>Current              | -          | 50       | -       | 80       | mA    |

| V <sub>CCS</sub> | Vcc Standby<br>Current            | -          | .3       | -       | .5       | mA    |

| V <sub>IL</sub>  | Input Low<br>Voltage              | -0.3       | .3 x Vcc | -0.3    | .3 x Vcc | V     |

| V <sub>IH</sub>  | Input High<br>Voltage             | 2.5        | Vcc + .3 | 2.5     | Vcc + .3 | V     |

| V <sub>OL</sub>  | Output Low<br>Voltage             | -          | .4       | -       | .4       | V     |

| V <sub>OH</sub>  | Output High<br>Voltage            | 2.4        | -        | 2.4     | -        | V     |

### SILICONSYSTEMS PROPRIETARY

### **AC CHARACTERISTICS**

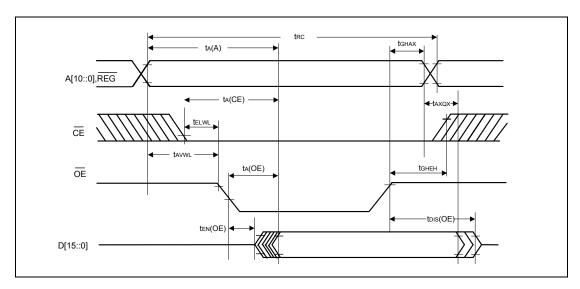

### **Attribute and Common Memory Read Timing**

Figure 2: Attribute and Common Memory Read Timing Diagram

Table 12: Attribute and Common Memory Read Timing

| Symbol                | Parameter                          | Minimum | Maximum | Units |

|-----------------------|------------------------------------|---------|---------|-------|

| t <sub>RC</sub>       | Read Cycle Time                    | 100     | -       | ns    |

| t <sub>A</sub> (A)    | Address Access Time                | -       | 100     | ns    |

| t <sub>A</sub> (CE)   | Card Enable Access Time            | -       | 100     | ns    |

| t <sub>A</sub> (OE)   | Output Enable Access Time          | -       | 50      | ns    |

| t <sub>DIS</sub> (OE) | Output Disable Time from OE        | -       | 50      | ns    |

| t <sub>EN</sub> (OE)  | Output Enable Time from OE         | 5       | -       | ns    |

| t <sub>AXQX</sub>     | Data Valid from Address Change     | 0       | -       | ns    |

| t <sub>AVWL</sub>     | Address Setup Time                 | 10      | -       | ns    |

| t <sub>AXQX</sub>     | Address Hold Time                  | 15      | -       | ns    |

| t <sub>ELWL</sub>     | Card Enable Setup Time before OE   | 0       | -       | ns    |

| t <sub>GHEH</sub>     | Card Enable Hold Time following OE | 15      | -       | ns    |

### SILICONSYSTEMS PROPRIETARY

This document and the information contained within it is confidential and proprietary to SiliconSystems, Inc.

All unauthorized use and/or reproduction is prohibited.

##

### **Attribute and Common Memory Write Timing**

Figure 3: Attribute and Common Memory Write Timing Diagram

Table 13: Attribute and Common Memory Write Timing

| Symbol            | Parameter                        | Minimum | Maximum | Units |

|-------------------|----------------------------------|---------|---------|-------|

| t <sub>WR</sub>   | Write Cycle Time                 | 100     | -       | ns    |

| t <sub>WLWH</sub> | Write Pulse Width                | 60      | -       | ns    |

| t <sub>AVWL</sub> | Address Setup Time               | 10      | -       | ns    |

| t <sub>AVWH</sub> | Address Setup Time for WE        | 70      | -       | ns    |

| t <sub>ELWH</sub> | Card Enable Setup Time for WE    | 70      | -       | ns    |

| t <sub>WHDX</sub> | Data Hold Time                   | 10      | -       | ns    |

| t <sub>WHAX</sub> | Write Recover Time               | 15      | -       | ns    |

| t <sub>WLQZ</sub> | Output Disable Time from WE      | -       | 75      | ns    |

| t <sub>OLWH</sub> | Output Disable Time from OE      | -       | 100     | ns    |

| t <sub>WHOX</sub> | Output Enable Time from WE       | 5       | -       | ns    |

| t <sub>OHDX</sub> | Output Enable Time from OE       | 5       | -       | ns    |

| t <sub>WLOL</sub> | Output Enable Setup for WE       | 10      | -       | ns    |

| t <sub>WHOL</sub> | Output Enable Hold from WE       | 10      | -       | ns    |

| t <sub>ELWL</sub> | Card Enable Setup Time before WE | 0       | -       | ns    |

| t <sub>GHEH</sub> | Card Enable Hold Time from WE    | 15      | -       | ns    |

| $t_{DVWH}$        | Data Setup Time                  | 40      | -       | ns    |

### SILICONSYSTEMS PROPRIETARY

This document and the information contained within it is confidential and proprietary to SiliconSystems, Inc.

All unauthorized use and/or reproduction is prohibited.

PAGE 18 MAY 22, 2007 DOCUMENT: SSDS04-3150C-R

## REG truca truc

### I/O Access Read Timing

Figure 4: I/O Access Read Timing Diagram

Table 14: I/O Access Read Timing

| Symbol              | Parameter                         | Minimum | Maximum | Units |

|---------------------|-----------------------------------|---------|---------|-------|

| t <sub>DVRL</sub>   | Data Delay after IORD             | -       | 50      | ns    |

| t <sub>IGHQX</sub>  | Data Hold following IORD          | 5       | -       | ns    |

| t <sub>IGLIGH</sub> | IORD Pulse Width                  | 65      | -       | ns    |

| t <sub>AVIGL</sub>  | Address Setup before IORD         | 25      | -       | ns    |

| t <sub>GHAX</sub>   | Address Hold following IORD       | 10      | -       | ns    |

| t <sub>CLIGL</sub>  | CE Setup before IORD              | 5       | -       | ns    |

| t <sub>CHIGH</sub>  | CE Hold following IORD            | 10      | -       | ns    |

| t <sub>RLIGL</sub>  | REG Setup before IORD             | 5       | -       | ns    |

| t <sub>RHIGH</sub>  | REG Hold following IORD           | 0       | -       | ns    |

| t <sub>IGLINL</sub> | INPACK Delay falling from IORD    | -       | (1)     | ns    |

| t <sub>IGHINH</sub> | INPACK Delay Rising from IORD     | -       | (1)     | ns    |

| t <sub>AVISL</sub>  | IOIS16 Delay Falling from Address | -       | (1)     | ns    |

| t <sub>AXISH</sub>  | IOIS16 Delay Rising from Address  | -       | (1)     | ns    |

Note: (1) IOIS16 and INPACK are not supported.

### SILICONSYSTEMS PROPRIETARY

This document and the information contained within it is confidential and proprietary to SiliconSystems, Inc.

All unauthorized use and/or reproduction is prohibited.

# REG touck touc

### I/O Access Write Timing

Figure 5: I/O Access Write Timing Diagram

Table 15: I/O Access Write Timing

| Symbol              | Parameter                         | Minimum | Maximum | Units |

|---------------------|-----------------------------------|---------|---------|-------|

| t <sub>IGHDX</sub>  | Data Hold following IOWR          | 5       | -       | ns    |

| t <sub>IGHQX</sub>  | Data Setup before IOWR            | 20      | -       | ns    |

| t <sub>IGLIGH</sub> | IOWR Pulse Width                  | 65      | -       | ns    |

| t <sub>AVIGL</sub>  | Address Setup before IOWR         | 25      | -       | ns    |

| t <sub>AXIGH</sub>  | Address Hold following IOWR       | 10      | -       | ns    |

| t <sub>CLIGL</sub>  | CE Setup before IOWR              | 5       | -       | ns    |

| t <sub>CHIGH</sub>  | CE Hold following IOWR            | 10      | -       | ns    |

| t <sub>RLIGL</sub>  | REG Setup before IOWR             | 5       | -       | ns    |

| t <sub>RHIGH</sub>  | REG Hold following IOWR           | 0       | -       | ns    |

| t <sub>AVISL</sub>  | IOIS16 Delay Falling from Address | -       | (1)     | ns    |

| t <sub>AXISH</sub>  | IOIS16 Delay Rising from Address  | -       | (1)     | ns    |

Note: (1) IOIS16 and INPACK are not supported.

### SILICONSYSTEMS PROPRIETARY

This document and the information contained within it is confidential and proprietary to SiliconSystems, Inc.

All unauthorized use and/or reproduction is prohibited.

PAGE 20 MAY 22, 2007 DOCUMENT: SSDS04-3150C-R

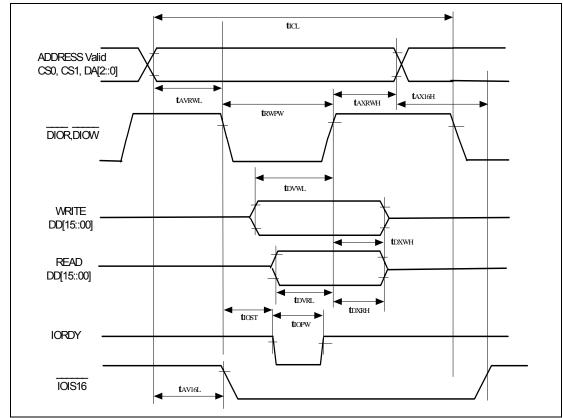

### **True IDE Read/Write Access Timing**

Figure 6: True IDE Read/Write Access Timing Diagram

Table 16: True IDE Read/Write Access Timing

| Symbol             | Parameter                              | Minimum | Maximum | Units |

|--------------------|----------------------------------------|---------|---------|-------|

| t <sub>ICL</sub>   | Cycle Time                             | 100     | -       | ns    |

| t <sub>AVRWL</sub> | Address Valid to DIOR, DIOW Setup Time | 15      | -       | ns    |

| t <sub>RWPW</sub>  | DIOR, DIOW Pulse Width                 | 65      | -       | ns    |

| $t_{DVWL}$         | DIOW Data Setup Time                   | 20      | -       | ns    |

| t <sub>DXWH</sub>  | DIOW Data Hold Time                    | 5       | -       | ns    |

| t <sub>DVRL</sub>  | DIOR Data Setup Time                   | 15      | -       | ns    |

| t <sub>DXRH</sub>  | DIOR Data Hold Time                    | 5       | -       | ns    |

| t <sub>AV16L</sub> | Address Valid to IOCS16 Assertion      | -       | (1)     | ns    |

| t <sub>AX16H</sub> | Address Valid to IOCS16 Negation       | -       | (1)     | ns    |

| t <sub>AXRWH</sub> | DIOW,DIOR to Address Valid Hold Time   | 10      | -       | ns    |

| t <sub>IOST</sub>  | IORDY Setup Time                       | -       | (1)     | ns    |

| t <sub>IOPW</sub>  | IORDY Pulse Width                      | -       | (1)     | ns    |

Note: (1) IOIS16 and INPACK are not supported.

### SILICONSYSTEMS PROPRIETARY

This document and the information contained within it is confidential and proprietary to SiliconSystems, Inc.

All unauthorized use and/or reproduction is prohibited.

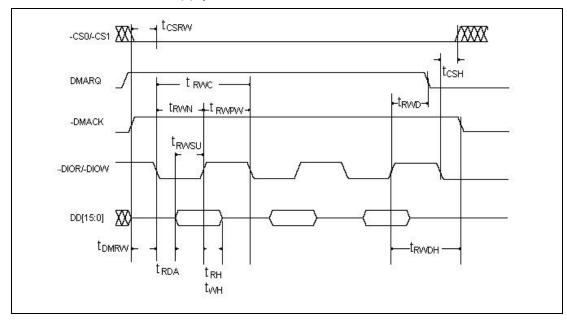

### True IDE Multiword DMA Read/Write Access Timing

This function does not apply to SiliconDrive Secures that have DMA disabled.

Figure 7: True IDE Multiword DMA Read/Write Access Timing

Table 17: True IDE Multiword DMA Read/Write Access Timing

| Symbol            | Parameter                     | Minimum | Maximum | Units |

|-------------------|-------------------------------|---------|---------|-------|

| t <sub>RWC</sub>  | Cycle Time (mode 2)           | 100     | -       | ns    |

| t <sub>RWPW</sub> | DIOR/DIOW Pulse Width         | 65      | -       | ns    |

| t <sub>RDA</sub>  | DIOR Data Access              | -       | 50      | ns    |

| t <sub>RWSU</sub> | DIOR/DIOW Data Setup Time     | 15      | -       | ns    |

| t <sub>WH</sub>   | DIOW Data Hold Time           | 5       | -       | ns    |

| t <sub>RH</sub>   | DIOR Data Hold Time           | 5       | -       | ns    |

| t <sub>DMRW</sub> | DMACK to DIOR/DIOW Setup Time | 0       | -       | ns    |

| t <sub>RWDH</sub> | DIOR/DIOW to DMACK Hold Time  | 5       | -       | ns    |

| t <sub>RWN</sub>  | DIOR/DIOW negated Pulse Width | 25      | -       | ns    |

| t <sub>RWD</sub>  | DIOR/DIOW to DMARQ Delay      | -       | 25      | ns    |

| t <sub>CSRW</sub> | CS(1:0) valid to DIOR/DIOW    | 10      | -       | ns    |

| t <sub>CSH</sub>  | CS(1:0) Hold Time             | 10      | -       | ns    |

### SILICONSYSTEMS PROPRIETARY

PAGE 22 MAY 22, 2007 DOCUMENT: SSDS04-3150C-R

### ATTRIBUTE MEMORY DESCRIPTION AND OPERATION

The attribute memory plane can be read or written to by asserting the REG# signal, qualified by the appropriate combination of CE1#, OE#, and WE#. An attribute memory map describing the type and location of the information maintained in the attribute memory plane is provided in "Attribute Memory Map" on page 25.

With respect to SiliconDrive Secure CF, attribute memory consists of two sections:

- Card Information Structure (CIS), which contains a description of the Card's capabilities and specifications.

- Function Configuration Registers (FCRs), which consists of four registers, that can be read or written to by a host to configure the Card for specific purposes.

### ATTRIBUTE MEMORY READ OPERATIONS

Attribute memory read operations are enabled by asserting REG#, OE#, and CE1# low. Odd byte read operations from the attribute memory plane are not valid.

Function REG# CE1# CE2# A0 OE# WE# D[15:8] D[7:0] Mode Χ Standby Н Н Χ Χ High-Z High-Z **Byte Access** L Н L L Н High-Z L Even L Н L Η L Н High-Z Not Valid Word Access L L Χ L Н Not Valid Even L Odd Byte Χ L L Н Н Н Not Valid High-Z Only Access

Table 18: Attribute Memory Read Operations

### SILICONSYSTEMS PROPRIETARY

DOCUMENT: SSDS04-3150C-R May 22, 2007 Page 23